Intellon's Mark Hazen Pg 24

EDN.comment: When Web sites go bad Pg 12

MAY

Issue 10/2008 www.edn.com

Bonnie Baker: Noise trade-offs Pg 26

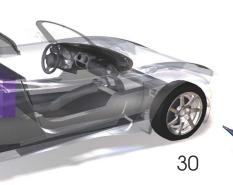

Prying Eyes: The Tesla Roadster: sporty and electric Pg 30

Design Ideas Pg 65

# FLEXIBLE SILICON

page 40

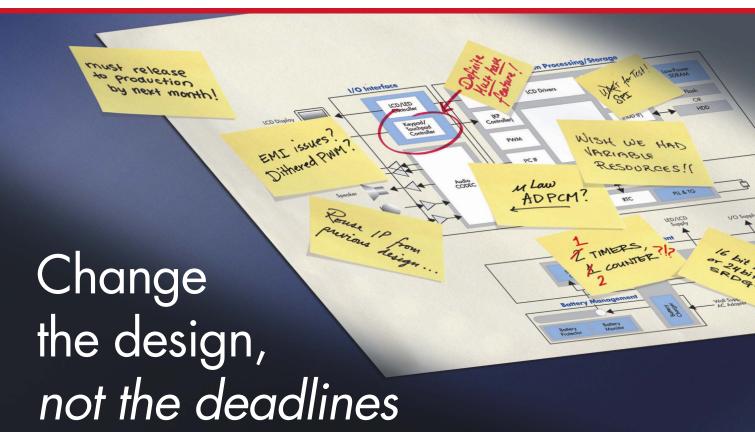

ALWAYS ON: EMBEDDING HIGH AVAILABILITY Page 33

1.1.1

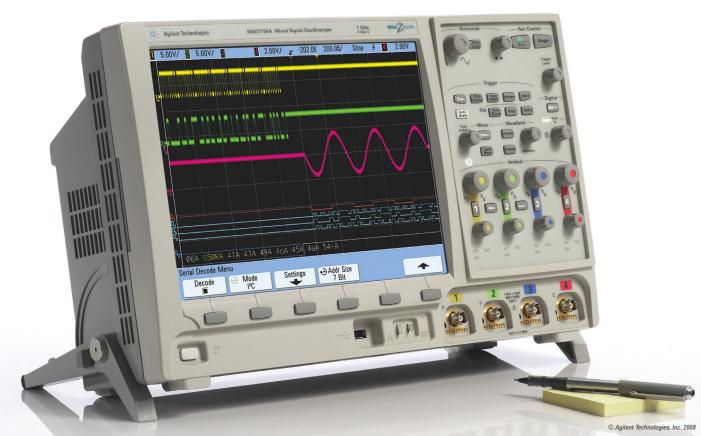

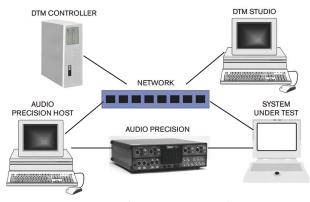

OVERCOMING USB MEASUREMENT-TEST-SETUP ISSUES

Page 49

TESTING YOUR NOTE-BOOK DESIGN FOR AUDIO FIDELITY

Page 55

CLICK HERE TO **START** a FREE <u>e-newsletter</u> subscription

CLICK HERE TO **RENEW** your FREE <u>magazine</u> subscription

# All the right tools in your hand.

### **WaveJet® Oscilloscopes**

#### More tools. Better tools. The right tools.

The right tools make debugging faster and easier. The WaveJet 300 Series provides more tools and greater performance than other compact oscilloscopes in the 100 MHz to 500 MHz range.

C1MΩ

- Long Memory: 500 k/ch

- Large 7.5" Color Display

- Compact Size, only 4" Deep

- USB Connectivity

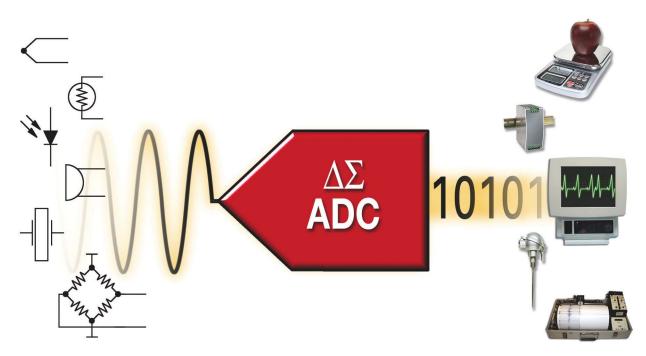

- Replay History Mode

- Frequency Counter

Hundreds-of thousands<sup>\*</sup> of parts in stock. Visit www.digikey.com today to see how many!

**Digi-Key Corporation purchases all product**

directly from its original manufacturer.

Quality Electronic Components, Superior Service

\*New product added daily. © 2008 Digi-Key Corporation

701 Brooks Ave. South • Thief River Falls, MN 56701 • USA

### Exclusively at Jameco... The Lowest Prices... Guaranteed!

#### Save 3% to 5%

Looking to save on thousands of Name Brand components? Jameco offers their popular products for 3% to 5% below market price, and we guarantee it!

#### Save 15%-25%

Save more when a specific manufacturer is not required. Major Brand semi's are sourced from 5-6 major manufacturers, plus we offer Jameco brand and generic passives for even greater savings.

#### Save 30% or more!

Looking for killer deals? Jameco buyers often find Factory Overruns from some of the industry's biggest names. That means savings of 30% and more to you!

### **Enter the New World of Bourns**

Automotive Sensors Circuit Protection Solutions Magnetic Products Microelectronic Modules Panel Controls & Encoders Precision Potentiometers Resistive Products The world of Bourns has grown. An expanding world focused on exceeding our customers' needs. New innovative products and technologies. Expanded application solutions. Plus a worldwide team of technical experts to facilitate the design process and solve tough application problems. All provided to

help customers shorten design cycles and achieve faster time-to-market.

At Bourns, we have grown to serve you better. Step in – explore the new world of possibilities from Bourns today:

www.bourns.com/newworld

Bourns - the company you have relied on for more than 60 years.

Built on Trust...Based on Innovation

# Green Engineering Powered by National Instruments

#### **MEASURE IT**

Acquire environmental data from thousands of sensors

Analyze power quality and consumption

Present measured data to adhere to regulations

FIX IT

Design and model more energy efficient machines

Prototype next-generation energy technologies

Deploy advanced controllers to optimize existing equipment

For more than 30 years, National Instruments has empowered engineers and scientists to measure, diagnose, and solve some of the world's most complex challenges. Now, through the NI graphical system design platform, engineers and scientists are using modular hardware and flexible software to not only test and measure but also fix inefficient products and processes by rapidly designing, prototyping, and deploying new machines, technologies, and methods. Today, a number of the world's most pressing issues are being addressed through green engineering applications powered by NI products.

#### >> Download green engineering resources at ni.com/greenengineering

#### 800 890 1345

#### Flexible silicon

4 O Evolving approaches to software development are providing designers with more flexibility in choosing and moving among processing choices.

by Robert Cravotta, Technical Editor

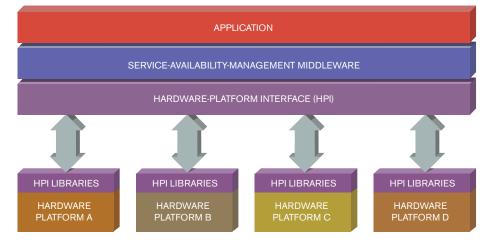

# Always on: embedding high availability

B Designers are tuning high-availability architectures to meet customer demands for a persistent data interface for the next generation of ultrareliable embeddedsystem applications.

by Warren Webb, Technical Editor

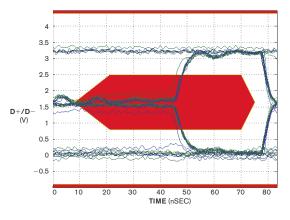

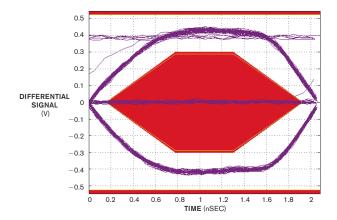

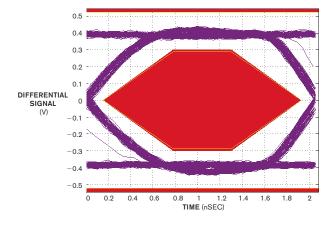

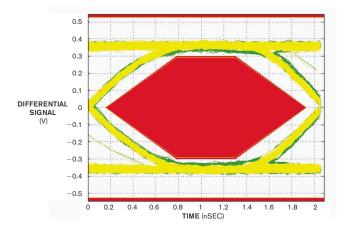

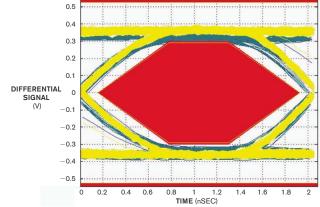

#### Overcoming USB measurement-testsetup issues

4 O Designers must meet stringent constraints to comply with the USB-IF spec. Clever techniques can help you design your system to meet these specs.

> by Keith Klepin, Cypress Semiconductor

#### Testing your notebook design for audio fidelity

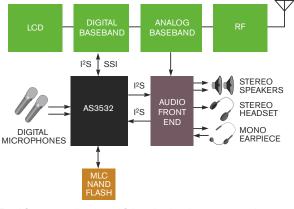

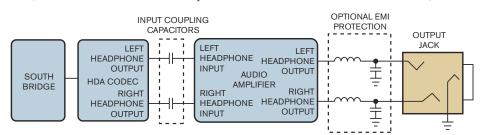

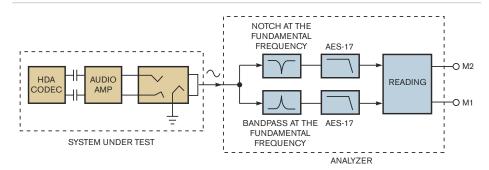

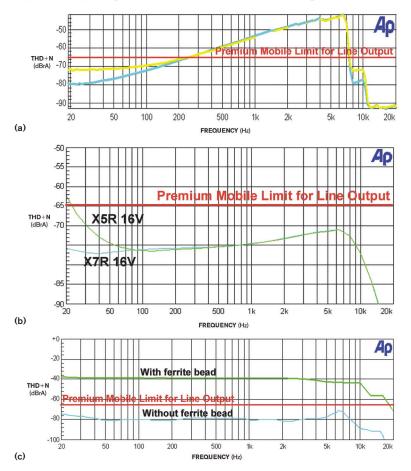

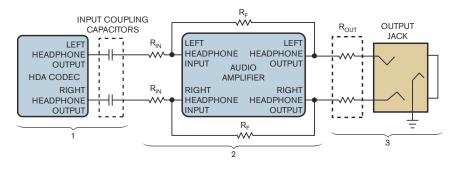

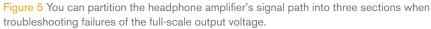

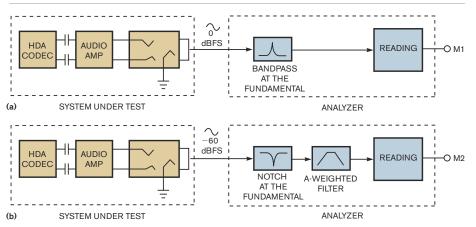

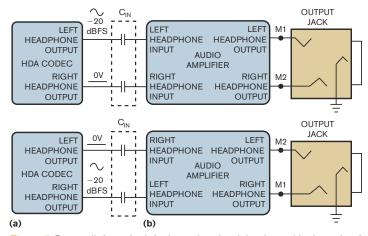

555 Program for the Vista operating system has introduced new audio-fidelity requirements for notebook PCs. Critical troubleshooting techniques can help you achieve compliance. by Kymberly Christman (Schmidt), Maxim Integrated Products

### DESIGNIDEAS

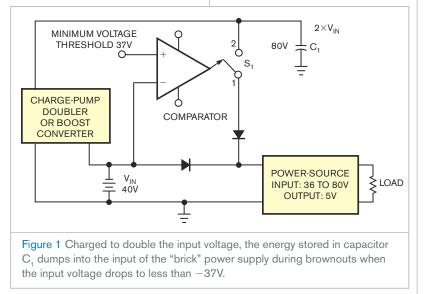

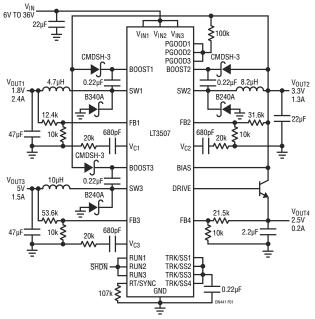

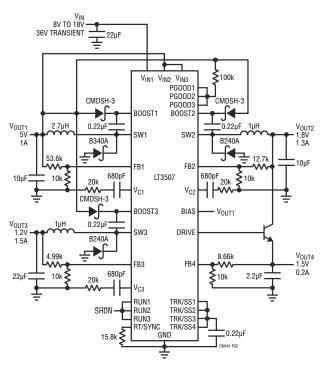

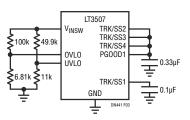

- 65 Small capacitor supports telecom power supply during brownouts

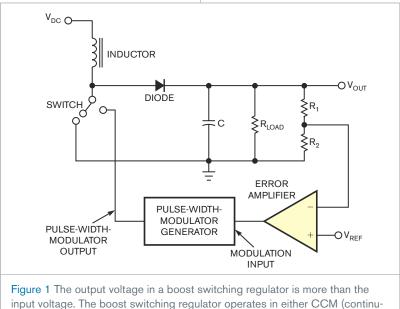

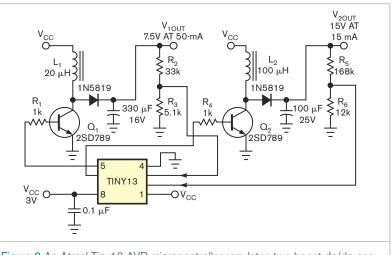

- 66 Tiny microcontroller hosts dual dc/dc-boost converters

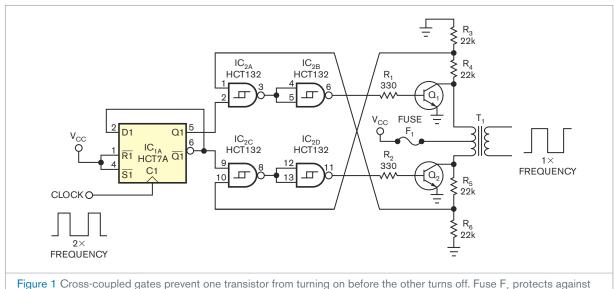

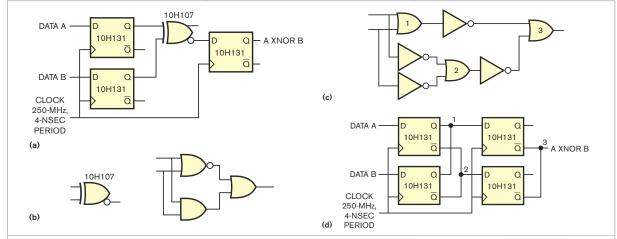

- 68 Cross-coupled gates prevent push-pull-driver overlap

- 70 Save valuable picoseconds using ECL-wired OR

#### WHAT DO WE HAVE TO DO, DRAW YOU A PICTURE?

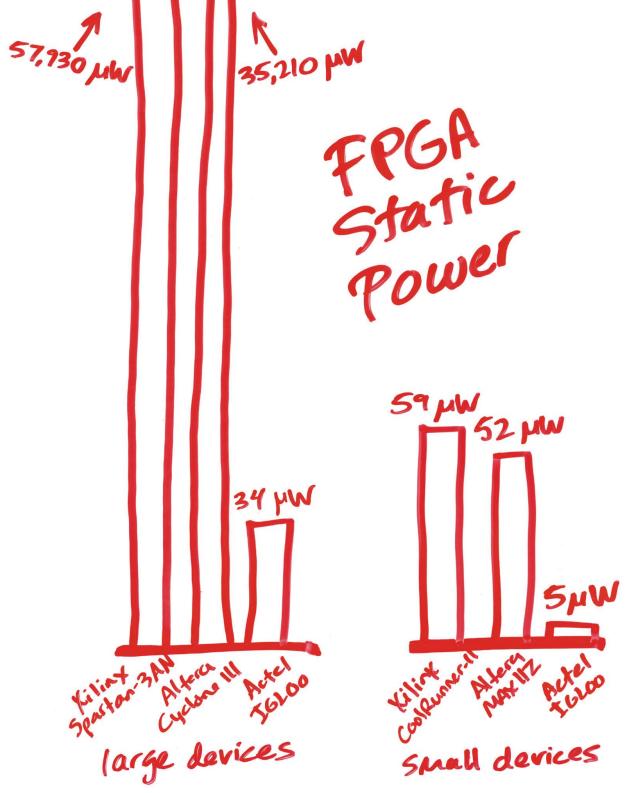

Only Actel gets you this close to zero. Any other claims of low power superiority are just that. According to their own data, Altera<sup>®</sup> and Xilinx<sup>®</sup> use between 10 and 1700 times the power of Actel IGLOO<sup>®</sup> FPGAs, depending on device and mode. Want specifics? Visit us to get the whole picture, including a video of actual measurements.

### contents 5.15.08

Dilbert 18

- 17 Stackable receiver enables position tracking

- 17 AMD releases dual- and triple-core desktop processors

- 18 Multiprocessor system sports as many as four coherent, multithreaded cores

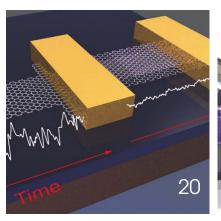

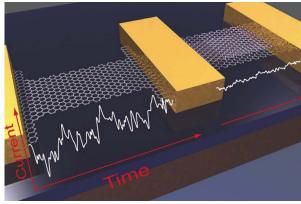

- 20 Atomic-sized graphene has use in nanoelectronics

- 20 Smart RFID chip automates data-logging, -tracking systems

- 22 Lossless coding comes to portables

- 22 CSR hits \$6 parts-cost for DSP-Bluetooth headset

- 24 **Voices:** Intellon's Mark Hazen on the HomePlug AV powerline-networking alternative

### DEPARTMENTS & COLUMNS

- 12 EDN.comment: When Web sites go bad

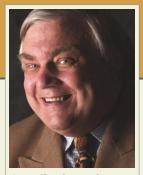

- 26 Baker's Best: RMS and peak-to-peak noise trade-off

- 28 **Tapeout:** Third-party-IP providers: physical-design questions, part one

- 30 **Prying Eyes:** The Tesla Roadster: sporty *and* electric

- 86 Tales from the Cube: Laser goes to (trim) pot

### PRODUCT ROUNDUP

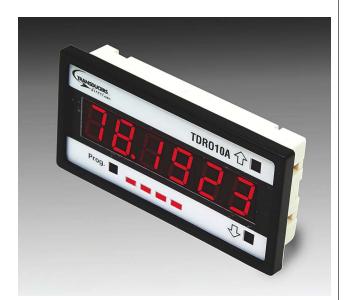

- 77 Sensors and Transducers: Programmable meters, proximity- and ambient-light sensors, Hall-effect sensors, GEM thermistors, and more

- 81 Microprocessors: FPGAs, ARM9 microcontrollers, development environments, high-end debuggers, 16-bit microcontrollers, and more

- 83 **Computers and Peripherals:** 1000W power supplies, LCDs, universal adapters, graphics cards, memory cards, RAID controllers, and more

EDN @ (ISSN#0012-7515), (GST#123397457) is published biweekly, 26 times per year, by Reed Business Information, 8878 Barrons Blvd, Highlands Ranch, CO 80129-2345. Reed Business Information, a division of Reed Elsevier Inc, is located at 360 Park Avenue South, New York, NY 10010. Tad Smith, Chief Executive Officer, Mark Finkelstein, President, Boston Division. Periodicals postage paid at Littleton, CO 80129 and additional maiing offices. Circulation records are maintained at Reed Business Information, 8878 S Barrons Blvd, Highlands Ranch, CO 80129-2345. Telephone (303) 470-4445. POSTMASTER: Send address changes to EDN & PO Box 7500, Highlands Ranch, CO 80129-2345. Telephone (303) 470-4445. POSTMASTER: Send address changes to EDN & PO Box 7500, Highlands Ranch, CO 80129-2345. Telephone (303) 470-4445. POSTMASTER: Send address changes to EDN & PO Box 7500, Highlands Ranch, CO 80129-2345. Telephone (303) 470-4445. POSTMASTER: Send address changes to EDN & PO Box 7500, Highlands Ranch, CO 80129-2345. Telephone (303) 470-4445. POSTMASTER: Send address changes to EDN & PO Box 7500, Highlands Ranch, CO 80129-2345. Telephone (303) 470-4445. POSTMASTER: Send address changes to EDN & PO Box 7500, Highlands Ranch, CO 80129-2345. Telephone (303) 470-4445. POSTMASTER: Send address changes to EDN & PO Box 7500, Highlands Ranch, CO 80129-2345. Telephone (303) 470-4445. POSTMASTER: Send address changes to ECR 510 telephone (303) 470-4445. POSTMASTER: Send Box 7500, Highlands Ranch, CO 80129-2345. EdN & Si to ESN 7500, Highlands Ranch, CO 80129-2345. EdN & Si to ESN 7500, Highlands Ranch, CO 80129-2345. EdN & Si to ESN 7500, Highlands Ranch, CO 80129-2345. EdN & Si to ESN 7500, Highlands Ranch, CO 80129-2345. EDN & Si a registered trademark of Reed Elsevier Properties Inc, used under license. A Reed Business Information Publication/Volume 53, Number 10 (Printed in USA).

# The Newest Embedded Technologies

# EMBEDDED CONTROL WAN WiFi • USB • BLUETOOTH<sup>™</sup> • ZIGBEE WLAN • NETWORK • USB • RFID • WAN UETOOTH<sup>™</sup> • EMBEDDED CONTROL • NETWORK FID • USB • WLAN • GPS • BLUETOOTH<sup>™</sup> ZIGBEE<sup>®</sup> • WIFI • EMERODED CONTROL

#### <u>New Products from:</u>

VDIP1 Module www.mouser.com/ftdi/a

RCM4000 RabbitCore® Modules www.mouser.com/rabbitsemi/a

MatchPort™ b/g Embedded Device Server www.mouser.com/lantronix/a

LANTRONIX

#### The ONLY New Catalog Every 90 Days

Experience Mouser's time-to-market advantage with no minimums and same-day shipping of the newest products from more than 335 leading suppliers.

a tti company

The Newest Products For Your Newest Designs

(800) 346-6873

Flexis<sup>™</sup> DemoQE128 Demo Board www.mouser.com/freescale/a

freescale

www.mouser.com

Over 965,000 Products Online

### online contents www.edn.com

номе

#### NEWS CENTER

DESIGN CENTERS

**BUSINESS CENTERS**

PART SEARCH

#### ONLINE ONLY

Check out these Web-exclusive articles:

#### Working group plans low-power serial-DRAM interface

Proposed SPMT (serial-port-memory technology) would start by drastically simplifying handset design. →www.edn.com/article/CA6555338

#### Triple core: Can AMD even the score?

Practically speaking, AMD needs to either get its clock speeds up to Intel levels or come up with a vastly more clock-efficient architecture to regain its standing as a solid competitor.

→www.edn.com/080515toc1

#### AMD: holes so big Intel could drive a truck through them

I'm starting to wonder whether Hector Ruiz and Bob Rivet were monks in a past life because they sure do have a vow-of-silence thing going on over at AMD. →www.edn.com/080515toc2

#### Software and hardware

Processor vendors now give support and development kits serious attention. →www.edn.com/080515toc3

#### ROHS: still debatable

Lead-free solder consumes more energy than tin/lead-based solder in the whole life cvcle, but there is no link between the harm to health and the environment and these solders, whereas the energy-consumption link to climate change is now almost proven.

→www.edn.com/080515toc4

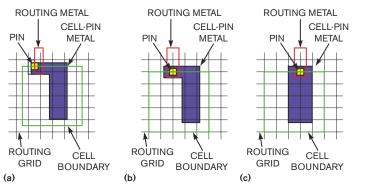

Is it an EDA tool or a manufacturing tool? Blaze DFM raises the question. →www.edn.com/080515toc5

#### READERS' CHOICE

A selection of recent articles receiving high traffic on www.edn.com.

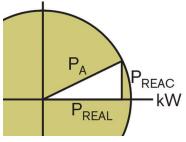

Honest energy: the danger low-powerfactor loads pose for the energy grid →www.edn.com/article/CA6544740

#### Boost efficiency

#### for low-cost flyback converters

Many devices employ flyback converters because of their simplicity and low costnot their stellar efficiency. But don't too quickly eliminate flybacks from your list of options. With a few little-known tricks, you can improve power loss by nearly 10%. →www.edn.com/article/CA6544742

#### Red LEDs function as light sensors

You can build simple LED illuminators using red LEDs to sense ambient-light level.

→www.edn.com/article/CA6541376

#### Blu-ray's triumph provides mixed blessings

From the beginning, all HD DVD players supported features that most Blu-ray players still don't implement: built-in Ethernet ports for easy upgrades, Webbased content augmentation, and rich user-interface interactivity.

→www.edn.com/080515toc7

#### Current source makes novel Class A buffer

A pair of classic current sources in a totem-pole configuration enables a novel Class A buffer.

→www.edn.com/article/CA6544738

#### PRYING EYES

#### An inside look at design decisions

In Prying Eyes, we peer inside an end-user gadget, a reference design, or any other interesting electronics-enabled thing we can get a good look at. Unlike your average billof-materials teardown, Prying Eyes aims to illuminate the tough design decisions the engineers responsible for the design had to make. Check out this month's installment on pg 30 and then visit the complete online Prying Eyes archive.

→www.edn.com/pryingeyes

# **Electronics Distributors**

Check out "The Impact of Technology Advancement on the Channel," an online-only supplement to EDN published in conjunction with the NEDA (National Electronic Distributors Association). Available as a 26-pg PDF, the supplement contains the Top 25 Electronics Distributors list, plus articles discussing the impact of environmental compliance and technology on the electronics supply chain. →www.edn.com/top25distributors

Your potential. Our passion.® **Microsoft**

#### FAST-FORWARD YOUR MASTERPIECE.

Get your next big idea to market—faster. The built-in tools and technologies in Windows® Embedded help to accelerate development, so your teams get to put their efforts where they really count: creating the next generation of smart, connected devices. You also get Windows Embedded features that enable interoperability with industry standards and Microsoft® technologies, so you can build devices that easily connect to PCs, services, servers, and other devices. Learn more about how to fast-forward device development at: windowsembedded.com/fastforward

# Windows<sup>®</sup> Embedded

#### BY PAUL RAKO, TECHNICAL EDITOR

### When Web sites go bad

ne of the most frustrating aspects of bad Web sites is that the contact links on the site all go to the Web team that screwed things up in the first place. Complaining to a Web team about its Web site is like complaining to the police about police brutality. My friend Dave, like all my analogdesign friends, is, well, a bit different. He has an electri-

cal-engineering degree but has spent most of his life as a software consultant. Dave is one of a few programmers I know who can program a Forth

kernel for a 16-bit microcontroller. He can also, for that matter, do high-level Web programming in Perl, SQL (Structured Query Language), C, or Visual Basic. He uses a Linux machine to do his Web browsing. He uses the Opera Web browser, working on a Linux box, because it is a cross-platform product. What exasperates Dave is how poorly most Web sites run on his Linux box. Dave is also a security nut. His wife works in the IT (information-technology) department of a major semiconductor company. She even served on the InterNIC (Internet-network-information-center) committee on Web security. Dave doesn't allow his Opera Web browser to run Java or JavaScript. He also doesn't allow the Web sites he visits to drop cookies onto his machine. And he doesn't run Adobe flash under Linux. All those snazzy flashanimated sites developed with Microsoft tools for Internet Explorer don't run well on Dave's machine.

Dave complains to the Web groups about how unusable their sites are, but they don't care. Worse yet, Dave's concerns never reach the company management. The Web team makes sure that it keeps any complaints from the A company that does not let the public complain directly to marketing, public relations, and top management will always have a crappy product.

management, and complaints die a nice, quiet death in the Web group's trash folder. A company that does not let the public complain directly to marketing, public relations, and top management will always have a crappy product. It is no different when the product is the company's Web site. It is not hard to craft a decent Web site. You can do it even with Microsoft tools, which work only with Microsoft servers and browsers. Tim Berners-Lee, the inventor of HTML (HyperText Markup Language) and key developer of the Internet, has given his support to the W3C (World Wide Web Consortium). It runs a validator page that makes sure that any Web site does not use Microsoft-exclusive code or bad HTML or XML (Extensible Markup Language, **Reference 1**). If your company's Web site runs on that validator, and it results in no errors, it is almost certain that the Web site will work on Windows, Linux, Macintosh, and most cell phones.

Now, I know that *EDN* drops cookies, but it is mostly so that we can tell whether you are a unique visitor or just refreshing the page. It gives us more accurate click counts. So, I am OK with cookies, but I sure have had my fill of JavaScript and flash. The pages of NBC Sports and other media giants are so software-intensive, they bring my CAD workstation to its knees.

Web teams should look to the Digi-Key Web site (www.digikey.com) to see something that just plain works. It is simple, some might even call it ugly, but it unfailingly delivers the goods. Web teams should also access their Web pages over a dial-up and a 384kbps DSL (digital-subscriber-line) modem. When I was at National Semiconductor, the Web team operated in the corporate headquarters and had a separate network that did not use the company's servers; it was just a DSL link to the outside world. The team staged any changes on hidden servers, tried everything out over the separate network, and put the pages out "live" only when the team members were happy. There would be a lot more good Web sites in the world if the complaint went to the chief executive officer rather than the webmaster.EDN

**REFERENCE** www.w3.org/QATools.

Contact me at paul.rako@edn.com.

#### MORE AT EDN.COM

+ Go to www.edn.com/080515ed and click on Feedback Loop to post a comment on this column.

| Part Number Search Search                 |  |

|-------------------------------------------|--|

| Search by                                 |  |

| Search     Search     O Inventory & quote |  |

# Their sites have search engines. Ours has a <u>find</u> engine.

| <u> </u>    |          |         |                    |                                          |              |              |                  |                   |           |           |                 |

|-------------|----------|---------|--------------------|------------------------------------------|--------------|--------------|------------------|-------------------|-----------|-----------|-----------------|

| Coil        | chi      | r l     | 4                  |                                          |              |              |                  |                   |           |           |                 |

| uu          | Nu       | ~0      |                    |                                          |              |              |                  |                   |           |           |                 |

| nduct       | or Fi    | nde     | er F               | Resi                                     | ults         | :            |                  |                   |           |           |                 |

|             |          |         |                    | n an | 1) DCI       |              | 2) -             | ¥                 | 3) -      | •         | Sort            |

| Part number | Mounting | Other ' | <b>L</b><br>* (μΗ) | DCR<br>(Ohms)                            | I sat<br>(A) | I rms<br>(A) | SI<br>(NL<br>DCI | -                 | W<br>(mm) | H<br>(mm) | Price<br>@1,000 |

| SER1360-182 | SM       | S       | 1.8                | 0.0024                                   | 18.0         | 13.0         | 50 Isat          | <del>к</del><br>К | 12.90     | 5.80      | \$0.67          |

| LPS5015-182 | SM       | S       | 1.8                | 0.0750                                   | 2.9          | 2.15         | 12 Irm           |                   | 5.00      | 1.50      | \$0.38          |

| LPS4414-182 | SM       | S       | 1.8                | 0.0870                                   | 2.9          | 1.9          | 13 Len           | _<br>gth          | 4.30      | 1.40      | \$0.38          |

| 1008PS-182  | SM       | S       | 1.8                | 0.0900                                   | 2.1          | 1.9          | 22 Wid           | lth               | 3.81      | 2.74      | \$0.64          |

| LPS3015-182 | SM       | S       | 1.8                | 0.1000                                   | 2.1          | 1.4          | 13 Pric          | yrit<br>:e        | 3.00      | 1.50      | \$0.38          |

| LPS3010-182 | SM       | S       | 1.8                | 0.1500                                   | 1.3          | 1.4          | 150.0            | 3.00              | 3.00      | 1.00      | \$0.38          |

| 0603PS-182  | SM       | S       | 1.8                | 0.5400                                   | 0.39         | 0.7          | 155.0            | 2.59              | 2.08      | 1.80      | \$0.51          |

| 1008LS-182  | SM       |         | 1.8                | 0.8400                                   |              | 0.6          | 170.0            | 2.92              | 2.79      | 2.03      | \$0.30          |

| 0603LS-182  | SM       |         | 1.8                | 1.1000                                   |              | 0.35         | 80.0             | 1.80              | 1.27      | 1.12      | \$0.41          |

| 0805LS-182  | SM       |         | 1.8                | 1.1500                                   |              | 0.41         | 246.0            | 2.29              | 1.91      | 1.60      | \$0.41          |

|             |          |         |                    |                                          |              |              |                  |                   |           |           |                 |

On most inductor web sites, their search engine results in more aggravation than answers.

But Coilcraft's web site is different.

In seconds, our Inductor Finder will show you all the parts that meet your electrical and size requirements. You can sort the results by your most important parameters. Compare pricing. Even analyze the core and winding losses of up to four different power inductors!

You'll find lots of other design tools to help you choose the perfect part. And then request free samples with just a few clicks.

So quit searching for magnetics and start finding them at **www.coilcraft.com**!

# **Beautify Your Eye On The Fly**

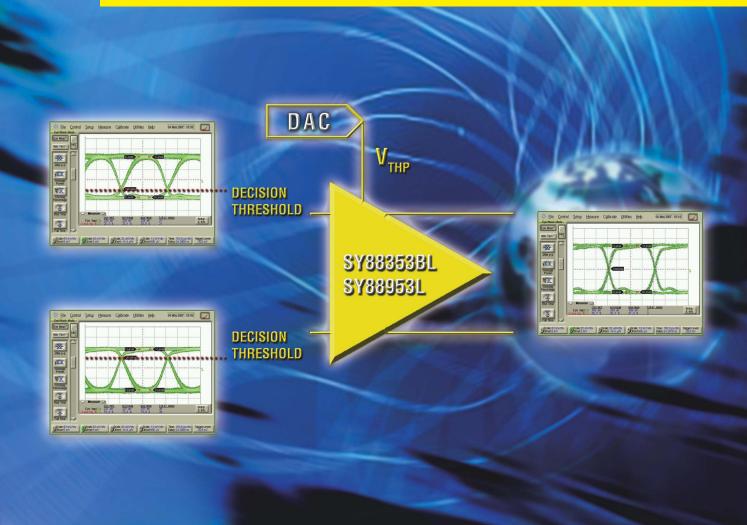

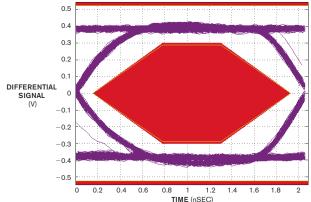

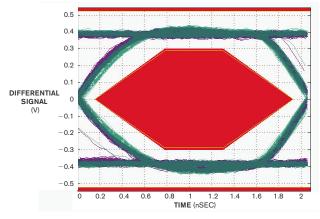

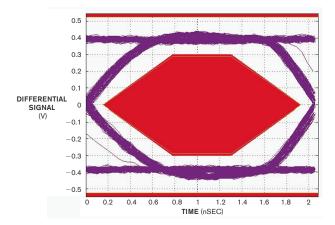

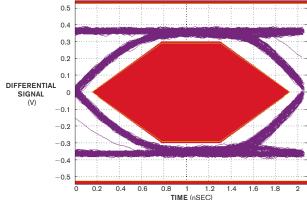

#### 3.3V, 3.2Gbps/10.7Gbps Limiting Post Amplifier with Programmable Decision Threshold

#### Key Benefits:

- Compensates for asymmetrical noise

- Eliminates input DC offsets in DC-coupled applications

- Decision threshold can be adjusted dynamically

- Minimizes jitter and improves BER

- Can improve sensitivity up to 3dBm

- ◆ Wide operating data range: 155Mbps 3.2Gbps/10.7Gbps

- ◆ Tiny 3mm x 3mm MLF<sup>®</sup> package to save space and cost

- ◆ Low-noise CML output with loss-of-signal indicator

For more information, contact your local Micrel sales representative or visit us at: www.micrel.com/ad/sy88353bl.

Applications Support & Evaluation Boards: 1(408) 955-1690, hbwhelp@micrel.com

#### Applications:

- ◆ WDM Systems

- SONET

- Fibre Channel

- Gigabit Ethernet

#### www.micrel.com

$\ensuremath{\textcircled{O}}$  2008 Micrel, Inc. All rights reserved. MLF is a registered trademark of Amkor Technology.

#### PRESIDENT, BOSTON DIVISION, REED BUSINESS INFORMATION Mark Finkelstein, mark.finkelstein@reedbusiness.com

1-781-734-8431

CONTRIBUTING TECHNICAL EDITORS Dan Strassberg, strassbergedn@att.net Nicholas Cravotta, editor@nicholascravotta.com

COLUMNISTS Howard Johnson, PhD; Bonnie Baker; Joshua Israelsohn; Pallab Chatteriee

#### PRODUCTION

Dorothy Buchholz, Group Production Director 1-781-734-8329 Kelly Jones, Production Manager 1-781-734-8328; fax: 1-303-265-3164 Linda Lepordo, Production Manager 1-781-734-8332; fax: 1-303-265-3015

#### EDN EUROPE

Graham Prophet, Editor, Reed Publishing The Quadrant, Sutton, Surrey SM2 5AS +44 118 935 1650; fax: +44 118 935 1670; gprophet@reedbusiness.com

#### EDN ASIA

Raymond Wong, Managing Director/ Publishing Director raymond.wong@rbi-asia.com Kirtimaya Varma, Editor in Chief kirti.varma@rbi-asia.com

EDN CHINA William Zhang, Publisher and Editorial Director wmzhang@idg-rbi.com.cn John Mu, Executive Editor iohnmu@ida-rbi.com.cn EDN JAPAN

Katsuya Watanabe, Publisher k.watanabe@reedbusiness.ip Ken Amemoto, Editor-in-Chief amemoto@reedbusiness.jp

The EDN Editorial Advisory Board serves as an industry touchstone for the editors of EDN worldwide, helping to identify key trends and voicing the concerns of the engineering community.

> DENNIS BROPHY Director of Business Development,

Mentor Graphics DANIS CARTER Principal Engineer, Tyco Healthcare

CHARLES CLARK

Technical Fellow, Pratt & Whitney Rocketdyne DMITRII LOUKIANOV

System Architect Intel RON MANCINI Retired Staff Scientist

GABRIEL PATULEA Design Engineer, Cisco

DAVE ROBERTSON

Product Line Director, Analog Devices SCOTT SMYERS

VP Network and System Architecture Division, Sony TOM SZOLYGA

Program Manager, Hewlett-Packard JIM WILLIAMS Staff Scientist, Linear Technology

EDN. 225 Wyman St, Waltham, MA 02451. www.edn.com. Phone 1-781-734-8000. Address changes or subscription inquiries: phone 1-800-446-6551; fax 1-303-470-4280; subsmail@reedbusiness.com.

PXI Source Measure Unit

#### Introducing Affordable Power and Precision in PXI

#### NI PXI-4130 SMU Features

- 4-quadrant operation up to +20 V and 2 A

- 1 nA measurement resolution

- Additional +6 V utility channel

- Compact size up to 17 SMU channels in a 19 in., 4U space

>> View product demos and download specifications at ni.com/smu

800 891 8841

©2008 National Instruments Corporation. All rights reserved. National Instruments, NI, and ni.com are trademarks of National Instruments. Other product and company names listed are trademarks or trade names of their respective comp 2007-9383-101-D

1-781-734-8307; fax: 1-303-265-3021; moleary@reedbusiness.com ANALOG Paul Rako, Technical Editor 1-408-745-1994: paul.rako@edn.com EMBEDDED SYSTEMS Warren Webb, Technical Editor 1-858-513-3713; fax: 1-858-486-3646; wwebb@edn.com MASS STORAGE, MULTIMEDIA, PCs, AND PERIPHERALS Brian Dipert, Senior Technical Editor 1-916-760-0159; fax: 1-303-265-3187; bdipert@edn.com MICROPROCESSORS, DSPs, AND TOOLS Robert Cravotta, Technical Editor 1-661-296-5096; fax: 1-303-265-3116; rcravotta@edn.com NEWS Suzanne Deffree, Managing Editor 1-631-266-3433; sdeffree@reedbusiness.com POWER SOURCES, ONLINE INITIATIVES Margery Conner, Technical Editor 1-805-461-8242; fax: 1-805-461-9640; mconner@reedbusiness.com SEMICONDUCTOR MANUFACTURING AND DESIGN Ann Steffora Mutschler, Senior Editor 1-408-345-4436; ann.mutschler@reedbusiness.com DESIGN IDEAS EDITOR Charles H Small edndesignideas@reedbusiness.com SENIOR ASSOCIATE EDITOR Frances T Granville, 1-781-734-8439;

PUBLISHER, EDN WORLDWIDE

Russell E Pratt. 1-781-734-8417:

rpratt@reedbusiness.com

ASSOCIATE PUBLISHER, EDN WORLDWIDE

Judy Hayes, 1-408-345-4437;

judy.hayes@reedbusiness.com

VICE PRESIDENT, EDITORIAL DIRECTOR

Karen Field, 1-781-734-8188;

kfield@reedbusiness.com

EDITOR-IN-CHIEF, EDN WORLDWIDE

Rick Nelson, 1-781-734-8418;

rnelson@reedbusiness.com

EXECUTIVE EDITOR

Ron Wilson, 1-408-345-4427;

ronald.wilson@reedbusiness.com

MANAGING EDITOR

Amy Norcross

1-781-734-8436; fax: 1-303-265-3017;

amy.norcross@reedbusiness.com

EDITOR-IN-CHIEF, EDN.COM

Matthew Miller

1-781-734-8446; fax: 1-303-265-3017;

mdmiller@reedbusiness.com

SENIOR ART DIRECTOR

Mike O'Leary

fax: 1-303-265-3131; f.granville@reedbusiness.com ASSOCIATE EDITOR Maura Hadro Butler, 1-617-276-6523;

mbutler@reedbusiness.com EDITORIAL/WEB PRODUCTION Diane Malone, Manager 1-781-734-8445; fax: 1-303-265-3024 Steve Mahoney, Production/Editorial Coordinator 1-781-734-8442: fax: 1-303-265-3198 Melissa Annand, Newsletter/Editorial Coordinator Contact for contributed technical articles 1-781-734-8443; fax: 1-303-265-3279 Adam Odoardi, Prepress Manager

1-781-734-8325; fax: 1-303-265-3042

For a free subscription, go to www.getfreemag.com/edn. Reed Business Information, 8878 S Barrons Blvd, Highlands Ranch, CO 80129-2345. Include your mailing label.

#### ACM/EDAC/IEEE 45th DESIGN AUTOMATION CONFERENCE JUNE 8-13, 2008 • ANAHEIM, CA • WWW.DAC.COM

# Where electronic design meets...

**Mark** your calendars for the 45th Design Automation Conference (DAC) at the Anaheim Convention Center, June 8-13, 2008, in Anaheim, California, USA.

#### **Only DAC Offers:**

- A robust technical program covering the latest research developments and trends for the design of SoCs, FPGAs, ASICs, digital ICs and more.

- Worldwide attendance from leading electronics companies and universities.

- Over 250 companies displaying electronic design technologies and services.

#### **Highlights Include:**

- Wireless Theme sessions

- Management Day on Tuesday, June 10

- Paper sessions featuring leading technical research

- New "iDesign" and WACI sessions

- Dynamic Panels Sessions

- DAC Pavilion Panels on the show floor

- 19 collocated events and workshops

- Full-day and Hands-on Tutorials

- New! Exhibitor Forum on the show floor

#### 2008 Keynotes:

- Justin R. Rattner, Intel Senior Fellow, Vice President, Director, Corporate Technology Group and Chief Technology Officer, Intel Corp.

*EDA for Digital, Programmable, Multi-Radios* Tuesday, June 10

- Sanjay K. Jha, COO and president of Qualcomm CDMA Technologies Challenges on Design Complexities for Advanced Wireless Silicon Systems Wednesday, June 11

- Jack Little, President, CEO, and a Co-founder of The MathWorks, Inc. *Idea to Implementation: A Different Perspective on System Design* Thursday, June 12

### Register on or before May 19th to receive 20% off Conference Registration or for a FREE Exhibit-Pass!

#### **REGISTER ON-LINE TODAY: www.dac.com**

©2008 Design Automation Conference

# **PERIPHERAL SUPPORT ICs**

#### UR SEMICONDUCTOR SOLUTIONS RESOURCE

Volume 8, Issue 3

#### Contents

*i*CMOS Switches and Multiplexers Enable Critical Systems Functions . . . . 1

Flexible Clocking Scheme for Multiple Wireless Standards ...... 3

Protect and Optimize Communications Networks with New Quad Channel Voltage Monitors and Sequencers .... 4

Low Power Comparators with Integrated Reference and Programmable Hysteresis . . . . . . 5

#### High Performance *i*CMOS<sup>®</sup> Switches and Multiplexers Enable Critical System Functions Everywhere

Analog Devices offers a broad portfolio of robust  $\pm 15$  V switches and multiplexers that are used in a wide range of applications where system reliability is critical, including industrial and instrumentation, medical, consumer, communications, and automotive systems. Leveraging the patented *i*CMOS manufacturing process technology, ADI's array of switches and multiplexers offers industry-leading performance in very small form factors to enable board area space savings.

#### **Automatic Test Equipment Applications**

For ATE applications with single-ended or differential inputs, ADI offers a choice of multiplexers with single four, eight, and 16 channels or differential four and eight channels. The ADG1406 is a  $\pm$ 15 V, 16:1 multiplexer, and the ADG1407 is a differential 8:1 multiplexer. Both offer low on resistance of 8  $\Omega$  with <1  $\Omega$  on-resistance flatness over the full signal range and are available in space-saving 5 mm  $\times$  5 mm LFCSP packages.

#### **Medical Applications**

In medical applications such as line-powered ECGs, where the requirements are generally for low R<sub>0N</sub>, dual-supply operation switches, the ADG1411 (4  $\times$  SPST) offers superior on resistance of 1.5  $\Omega$  and R<sub>0N</sub> flatness of 0.28  $\Omega$  over the full signal range. This level of performance assists in minimizing signal loss and distortion of the signal through the switch—especially important when switching gains for op amps. The ADG1411 is available in 4 mm  $\times$  4 mm LFCSP packaging, suitable for both portable and benchtop systems.

#### **Industrial Applications**

Industrial design engineers require analog switches that support faster sampling, increased performance, lower power dissipation, and a smaller footprint. The ADG1201 SPST and ADG1219 SPDT switches meet these requirements by offering ultralow capacitance, charge injection, and leakage at  $\pm$ 15 V operation. Both have <1 pC charge injection and low leakage of <1 nA at 125°C and are available in tiny 6-lead SOT-23 packages.

| For more information, go to | www.analog.com/icmos. |

|-----------------------------|-----------------------|

|-----------------------------|-----------------------|

| Part Number                     | Function                      | <b>R<sub>oN</sub> Typ</b><br>(Ω) | Q <sub>⊪J</sub> Typ<br>(pC) | On Leakage<br>Typ (nA) | Package<br>(mm)           | Price<br>(\$U.S.) |

|---------------------------------|-------------------------------|----------------------------------|-----------------------------|------------------------|---------------------------|-------------------|

| ADG1201,<br>ADG1202             | 1 	imes SPST, NC, NO          | 120                              | 0.3                         | 0.02                   | 6-lead SOT-23             | 1.01              |

| ADG1411,<br>ADG1412,<br>ADG1413 | 4 $	imes$ SPST, NO, NC, NO/NC | 1.5                              | 20                          | 0.2                    | TSSOP, $4 	imes 4$ LFCSP  | 2.66              |

| ADG1406,<br>ADG1407             | 16:1, diff 8:1 mux            | 8                                | 50                          | 0.04                   | TSSOP, $5 \times 5$ LFCSP | 4.81              |

Order this valuable design resource to help optimize your PC board designs.

**REE OFFER**

www.analog.com/V8Peripherals

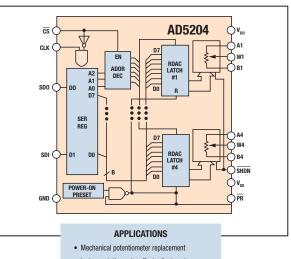

### Quad Channel, 256-Position Digital Potentiometers in 5 mm $\times$ 5 mm QFN Packaging Significantly Reduce Board Space

A digital potentiometer adjusts and trims electronic circuits in the same way that variable resistors, rheostats, and mechanical potentiometers do. These compact devices can be used to calibrate system tolerances or dynamically control system parameters in cases where a fine-tuned analog output is controlled by a digital input.

The AD5204 provides 4-channel, 256-position, digitally controlled variable resistor (VR) devices. These devices perform the same electronic adjustment function as a potentiometer or variable resistor. Each channel of the AD5204 contains a fixed resistor with a wiper contact that taps the fixed resistor value at a point determined by a digital code loaded into the SPI-compatible serial input register. The resistance between the wiper and either endpoint of the fixed resistor varies linearly with respect to the digital code

transferred into the VR latch. The variable resistor offers a completely programmable value of resistance between the A terminal and the wiper or the B terminal and the wiper. The fixed A-to-B terminal resistance of 10 k $\Omega$ , 50 k $\Omega$ , or 100 k $\Omega$  has a nominal temperature coefficient of 700 ppm/°C. Each VR has its own VR latch, which holds its programmed resistance value. These VR latches are updated from an internal serial-to-parallel shift register that is loaded from a standard 3-wire serial input digital interface. Eleven data bits make up the data word clocked into the serial input register. The first three bits are decoded to determine which VR latch will be loaded with the last eight bits of the data word when the CS strobe is returned to logic high. A serial data output pin at the opposite end of the serial register (AD5204 only) allows simple daisy-chaining in multiple VR applications without additional external decoding logic. The AD5206 is a 6-channel solution.

Packaging options help you to address your system requirement trade-offs including device cost and board area. Options for both the AD5204 and AD5206 include 24-lead SOIC, TSSOP, and PDIP packages. The AD5204 is also available in 5 mm  $\times$  5 mm LFCSP for the most popular 10 k $\Omega$  resistor value.

- Instrumentation gain, offset adjustment

- Programmable voltage-to-current conversion

Programmable filters, delays, time constants

- Line impedance matching

| Part<br>Number | Number of<br>Channels | Number of<br>Positions | Memory<br>Type   | Interface                          | Resistor Values (k $\Omega$ ) | Voltage<br>Range (V) | Temperature<br>Range (°C) | Absolute Tempco<br>(ppm/°C) | Price<br>(\$U.S.) |

|----------------|-----------------------|------------------------|------------------|------------------------------------|-------------------------------|----------------------|---------------------------|-----------------------------|-------------------|

| AD5203         | 4                     | 64                     | Volatile         | SPI                                | 10, 100                       | 5.5                  | -40 to +85                | 700                         | 1.45              |

| AD5204         | 4                     | 256                    | Volatile         | SPI                                | 10, 50, 100                   | ±3, 5.5              | -40 to +85                | 700                         | 1.50              |

| AD8403         | 4                     | 256                    | Volatile         | SPI                                | 1, 10, 50, 100                | 5.5                  | -40 to +125               | 500                         | 2.76              |

| AD5263         | 4                     | 256                    | Volatile         | I <sup>2</sup> C, <sup>®</sup> SPI | 20, 50, 200                   | ±5, 15               | -40 to +125               | 30                          | 2.55              |

| AD5206         | 6                     | 256                    | Volatile         | SPI                                | 10, 50, 100                   | ±3, 5.5              | -40 to +85                | 700                         | 1.92              |

| AD5233         | 4                     | 64                     | Non-<br>volatile | SPI                                | 1, 10, 50, 100                | ±3, 5.5              | -40 to +85                | 600                         | 2.47              |

| AD5253         | 4                     | 64                     | Non-<br>volatile | I <sup>2</sup> C                   | 1, 10, 50, 100                | ±3, 5.5              | -40 to +85                | 300                         | 2.46              |

| AD5254         | 4                     | 256                    | Non-<br>volatile | I <sup>2</sup> C                   | 1, 10, 50, 100                | ±3, 5.5              | -40 to +85                | 300                         | 2.55              |

#### PCB Design Resource

#### Order Yours Today

#### www.analog.com/V8Peripherals

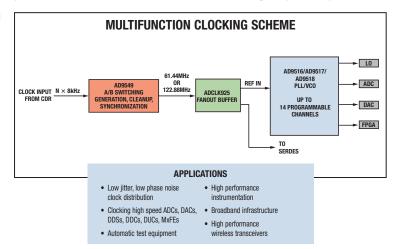

#### Flexible Clocking Scheme Accommodates Multiple Wireless Standards

To establish a clean and stable clock in wireless systems, designers typically employ a standard set of multiple discrete components including FPGA, filters, VCXO, PLL, and various clock distribution circuitry. However, this approach is undesirable because it often yields a complicated, high cost, low reliability clocking scheme, and consumes a large portion of the PCB area. In contrast, integrating critical timing functions onto higher function clock devices translates to using fewer components for lower overall cost, increased reliability, and a smaller footprint. As shown in the diagram below, multiple clock ICs may be combined to form a complete multifunction timing solution that addresses clock cleanup, generation, synchronization, and distribution, to meet the most stringent system requirements.

In a remote radio unit (RRU), the incoming signal is cleaned up and then delivered to a clock generator to translate the frequency outputs to other system components. The ultraclean signal from the buffer goes through a SERDES to be sent back upstream. This clocking platform is ideal for digitizing a signal across multiple wireless standards, such as WiMAX, W-CDMA, CDMA2000, and CDMA.

The AD9549 clock generator/synchronizer cleans up a CDR clock using a digital PLL with a programmable loop bandwidth down to 0.1 Hz. The device provides reference monitoring and holdover functions. It delivers integrated jitter of <1 ps rms.

An ultrafast 1:2 clock buffer, the ADCLK925, boasts fast output rise and fall times of 60 ps to maximize bandwidth and signal integrity. In addition, only 60 fs of random jitter is added on the outputs. The buffer distributes clean copies of the signal to both a SERDES and a flexible multioutput clock generator.

The AD9516, AD9517, and AD9518, all with on-chip VCXO, offer excellent close-in phase noise performance when clocking multiple system components. The flexibility in selecting from multiple logic types and frequency combinations creates an ideal solution that can be used in various wireless systems. Five versions of each product are available with VCOs tuned from 1.45 GHz to 2.95 GHz.

#### **Clock Generation ICs**

| Part Number | Outputs                    | Dividers | Delay Lines | Package                          | Price (\$U.S.) |

|-------------|----------------------------|----------|-------------|----------------------------------|----------------|

| AD9516-x    | 6 LVPECL,<br>4/8 LVDS/CMOS | 5        | 4           | 9 mm $	imes$ 9 mm, 64-lead LFCSP | 12.50          |

| AD9517-x    | 4 LVPECL,<br>4/8 LVDS/CMOS | 4        | 4           | 7 mm $	imes$ 7 mm, 48-lead LFCSP | 11.40          |

| AD9518-x    | 6 LVPECL                   | 3        | None        | 7 mm $	imes$ 7 mm, 48-lead LFCSP | 9.85           |

#### **Clock Buffers**

| Part<br>Number | Number of<br>Inputs | Number of<br>Outputs | Max Clock<br>Input (GHz) | Output Logic      | Random Jitter<br>(ps rms) | Price (\$U.S.) |

|----------------|---------------------|----------------------|--------------------------|-------------------|---------------------------|----------------|

| ADCLK905       | 1                   | 1                    | 6                        | ECL, PECL, LVPECL | 0.06                      | 5.60           |

| ADCLK907       | 2                   | 2                    | 6                        | ECL, PECL, LVPECL | 0.06                      | 6.75           |

| ADCLK914       | 1                   | 1                    | 6                        | HVDS              | 0.1                       | 6.95           |

| ADCLK925       | 1                   | 2                    | 6                        | ECL, PECL, LVPECL | 0.06                      | 5.95           |

Design the jitter out of your circuit with the help of ADI's ADIsimCLK<sup>™</sup> free online design tool. To begin, visit *www.analog.com/ADIsimCLK*. "Network Clock: How to Achieve Maximum System Up Time" at www.analog.com/onlineseminars.

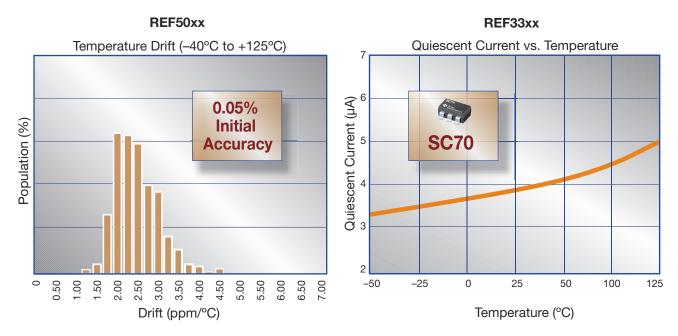

#### **Optimizing Signal Chain Performance with Voltage References**

As a point of reference for converter accuracy, voltage references play a critical role in overall system performance. Providing the comparison for all other measurements, a voltage reference's accuracy, noise, and stability (among other specifications) are vital to allowing the converter to produce an accurate measurement (for ADC) or output (for DAC). Using a discrete voltage reference is often desirable when best-in-class tempco, hysteresis, and long-term drift performance are important to the application. Analog Devices offers a wide range of voltage references, from <3 ppm/°C for test, measurement, and instrumentation applications to >50 ppm/°C for power delivery and power management applications.

| Part<br>Number            | <b>V</b> <sub>0</sub> ( <b>V</b> )   | Initial<br>Accuracy (%) | Tempco<br>(ppm/°C)  | Output Noise<br>(µV p-p) | Supply<br>Voltage (V) | Package                                      | Price<br>(\$U.S.) |

|---------------------------|--------------------------------------|-------------------------|---------------------|--------------------------|-----------------------|----------------------------------------------|-------------------|

| ADR121, ADR125,<br>ADR127 | 2.5, 5, 1.25                         | 0.12, 0.24              | 9, 25               | 10, 20, 5                | 2.7 to 18             | 6-lead TSOT                                  | 0.77, 1.19        |

| ADR130                    | 0.5, 1                               | 0.35, 0.7               | 25, 50              | 3, 6                     | 2 to 18               | 6-lead TSOT                                  | 0.97, 1.25        |

| ADR42x, ADR43x,<br>ADR44x | 2.048, 2.5, 3,<br>4.096, 4.5, 5      | 0.05, 0.15              | 3, 10               | 1 to 7.5                 | 4.5 to 18             | 8-lead MSOP,<br>8-lead SOIC                  | 2.65, 3.05        |

| AD586                     | 5                                    | 0.04, 0.05,<br>0.1, 0.2 | 2, 5, 10            | 4                        | 10 to 36              | 8-lead PDIP,<br>8-lead SOIC                  | 2.86, 6.91        |

| REF19x                    | 2.048, 2.5, 3, 3.3,<br>4.096, 4.5, 5 | 0.04,<br>0.33           | 2, 5, 10,<br>20, 25 | 20 to 50                 | 3 to 15               | 8-lead PDIP,<br>8-lead SOIC,<br>8-lead TSSOP | 1.36, 2.59        |

"Driving Precision Converters: How to Select the Best Voltage Reference and Amplifier for Your ADC Application" at www.analog.com/onlineseminars.

#### Protect and Optimize Communications Networks with ADI's New Family of 0.8% Accuracy, Quad Channel Voltage Monitors and Sequencers

Analog Devices introduces several new quad voltage monitors and sequencers with industry-leading, highest accuracy threshold accuracy (0.8%). The 0.8% threshold accuracy specification allows low voltage rails (~1 V) to be accurately monitored and sequenced. The ADM1186 allows power-up and power-down (reverse order) sequencing in hardware using resistors and capacitors. No software support is required. Correct power supply sequencing ensures that the power supply rails come up and are powered down in the correct order and that each rail is within tolerance ensuring more reliable system performance. The cascadability of these devices provides power up and down (reverse sequence) of more than four voltage rails by cascading multiple devices. External capacitors define the time delay between the voltage rails turning on during the power-up sequence and turning the power supplies off during the power-down sequence.

| Part      | Number of     | Voltage | Number               | Sequencing |      | Enable     | Sequence |              | Price    |  |

|-----------|---------------|---------|----------------------|------------|------|------------|----------|--------------|----------|--|

| Number    | Sunnlies Mo   |         | of Output<br>Drivers | Up         | Down | Output     | Delay    | Package      | (\$U.S.) |  |

| ADM1184   | 4: cascadable | <0.8%   | 4                    | Yes        | No   | Open-drain | —        | 10-lead MSOP | 2.39     |  |

| ADM1185   | 4: cascadable | <0.8%   | 4                    | Yes        | No   | Open-drain | 190 ms   | 10-lead MSOP | 1.20     |  |

| ADM1186-1 | 4: cascadable | <0.8%   | 4                    | Yes        | Yes  | Open-drain | Cap adj  | 20-lead QSOP | 3.80     |  |

| ADM1186-2 | 4             | <0.8%   | 4                    | Yes        | Yes  | Open-drain | Cap adj  | 16-lead QSOP | 2.98     |  |

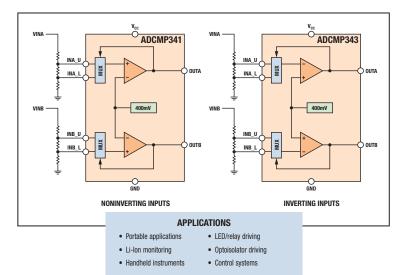

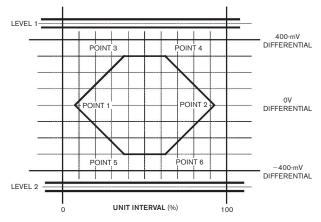

#### ADI Continues to Grow Its Low Power Comparator Portfolio with Dual Comparators that Feature Integrated Reference and Programmable Hysteresis

Lower power comparators are ideal for power sensitive applications such as battery-powered equipment. The ADCMP341 and ADCMP343 ICs combine two low power, low voltage comparators with a 400 mV reference in a tiny 5-lead SOT-23 package. Operating within a supply range of 1.7 V to 5.5 V, the devices only draw 6.5  $\mu$ A typical—making them ideal for low voltage system monitoring and portable applications. Hysteresis is determined using three resistors in a string configuration with the upper and lower tap points connected to the INA\_U and INA\_L pins of each comparator, respectively. The comparator's output internally selects which pin is connected to the comparator inputs. A change of state in the comparator output will result in one of the inputs being switched into the comparator outputs are open-drain with the output stage sinking capability guaranteed greater than 5 mA over temperature. In addition, this IC family offers various features depending upon the design need—for example, the ADCMP341 has noninverting inputs while the ADCMP343 has inverting inputs. The devices are available in commercial, industrial, and automotive temperature ranges. For a complete listing of ADI comparators, visit *www.analog.com/comparators*.

#### Low Power Comparator Family Features

- Low quiescent current: 6.5 μA typical

- Supply range: 1.7 V to 5.5 V

- 400 mV reference: ±0.275% threshold accuracy

- Input range includes ground

- User programmable hysteresis via resistor string

- Low input bias current: ±5 nA maximum

- · Open-drain outputs

- Supports wire-AND'ed connections

- · Input polarities (noninverting and inverting)

- Package: small, 8-lead SOT-23

| Part<br>Number | Number<br>per<br>Package | Reference<br>Accuracy<br>(±%) | Supply<br>Voltage (V) | Logic I/O                  | Input<br>Range (V) | Propagation<br>Delay Typ<br>(µs) | Hysteresis | Package       | Price<br>(\$U.S.) |

|----------------|--------------------------|-------------------------------|-----------------------|----------------------------|--------------------|----------------------------------|------------|---------------|-------------------|

| ADCMP341       | 2                        | 0.275                         | 1.7 to 5.5            | Open-drain                 | 0 to $V_{cc}$      | 10.0                             | Adjustable | 8-lead SOT-23 | 0.90              |

| ADCMP343       | 2                        | 0.275                         | 1.7 to 5.5            | Open-drain                 | 0 to $V_{cc}$      | 10.0                             | Adjustable | 8-lead SOT-23 | 0.90              |

| ADCMP350       | 1                        | 3.5                           | 2.25 to 5.5           | Open-drain,<br>active low  | 0 to 22            | 5.0                              | Internal   | 4-lead SC70   | 0.31              |

| ADCMP354       | 1                        | 3.5                           | 2.25 to 5.5           | Open-drain,<br>active high | 0 to 22            | 5.0                              | Internal   | 4-lead SC70   | 0.31              |

| ADCMP356       | 1                        | 3.5                           | 2.25 to 5.5           | Push-pull, active high     | 0 to 22            | 5.0                              | Internal   | 4-lead SC70   | 0.31              |

| ADCMP361       | 1                        | 0.275                         | 1.7 to 5.5            | Open-drain                 | 0 to $V_{cc}$      | 10.0                             | Internal   | 5-lead SOT-23 | 0.60              |

| ADCMP370       | 1                        |                               | 2.25 to 5.5           | Open-drain                 | 0 to 22            | 5.0                              | Internal   | 5-lead SOT-23 | 0.28              |

| ADCMP371       | 1                        | —                             | 2.25 to 5.5           | Push-pull                  | 0 to 22            | 5.0                              | Internal   | 5-lead SOT-23 | 0.28              |

| ADCMP670       | 2                        | 1.50                          | 1.7 to 5.5            | Open-drain                 | 0 to 6             | 10.0                             | Internal   | 6-lead SOT-23 | 1.40              |

| CMP04          | 4                        | —                             | 5                     | Open-<br>collector         | $V_{cc}$ to 1.5    | 1.3                              | —          | 14-lead SOIC  | 4.75              |

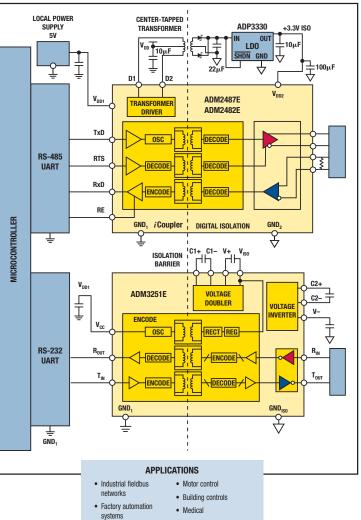

### Protect Your Valuable Communications Networks with ADI's Family of RS-232 and RS-485 Digitally Isolated ICs

The RS-485 and RS-232 bus standards are the most widely used physical layer bus designs in industrial and instrumentation and medical applications. To improve system reliability within a noisy environment and protect against voltage spikes and ground loops, isolation is required between the RS-485/RS-232 cable network and the systems connected to it. Power isolation is obtained through the use of an isolated dc-to-dc power supply or Analog Devices *iso*Power<sup>®</sup> integrated dc-to-dc converters. Signal isolation is implemented using Analog Devices' *i*Coupler<sup>®</sup> technology. ADI provides integrated isolated RS-485 and RS-232 transceivers to solve these problems.

In addition, visit *www.analog.com/rs485* and *www.analog.com/rs232* for more information.

| Part<br>Number | Protocol | FD/HD | Data<br>Rate | Isolation<br>Rating (V rms) | Temperature<br>Range (°C) | Integrated <i>iso</i> Power | Integrated<br>Transformer<br>Driver | Package         | Price<br>(\$U.S.) |

|----------------|----------|-------|--------------|-----------------------------|---------------------------|-----------------------------|-------------------------------------|-----------------|-------------------|

| ADM2483        | RS-485   | HD    | 500 kbps     | 2500                        | -40 to +85                | No                          | No                                  | 16-lead wide SO | 3.00              |

| ADM2485        | RS-485   | HD    | 16 Mbps      | 2500                        | -40 to +85                | No                          | Yes                                 | 16-lead wide SO | 5.50              |

| ADM2486        | RS-485   | HD    | 20 Mbps      | 2500                        | -40 to +85                | No                          | No                                  | 16-lead wide S0 | 4.98              |

| ADM2490E       | RS-485   | FD    | 16 Mbps      | 5000                        | -40 to +105               | No                          | No                                  | 16-lead wide SO | 4.50              |

| ADM2491E       | RS-485   | FD/HD | 16 Mbps      | 5000                        | -40 to +85                | No                          | No                                  | 16-lead wide SO | 4.70              |

| ADM2487E       | RS-485   | FD/HD | 500 kbps     | 2500                        | -40 to +85                | No                          | Yes                                 | 16-lead wide SO | 3.60              |

| ADM2482E       | RS-485   | FD/HD | 15 Mbps      | 2500                        | -40 to +85                | No                          | Yes                                 | 16-lead wide SO | 4.60              |

| ADM3251E       | RS-232   | —     | 460 kbps     | 2500                        | -40 to +85                | Yes                         | No                                  | 20-lead wide S0 | 2.99              |

#### PCB Design Resource Order Yours Today

#### www.analog.com/V8Peripherals

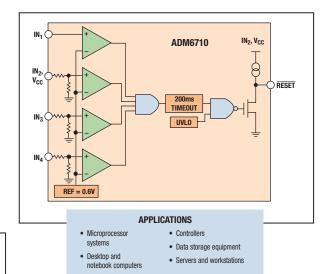

### ADI's High Accuracy Multivoltage Supervisor ICs Monitor Low Voltage Core Supplies for Peak Performance

Accurately monitoring the supply voltage of a microprocessor is critical to achieving the levels of performance and output required by today's sophisticated electrical equipment. To meet these needs, ADI's family of voltage monitors includes dual, triple, and quad variants that accommodate a wide range of voltage inputs.

The ADM6710 is a low voltage, high accuracy, microprocessor supervisory circuit capable of monitoring up to four system supply voltages. Should an input drop below its associated threshold, an active low output asserts. The output is open-drain with a weak internal pull-up to the monitored IN2 or  $V_{cc}$  supply, typically 10  $\mu$ A. Subsequent to all voltages rising above the selected threshold, the reset remains low for the reset timeout period (140 ms minimum).

#### ADM6710 Features

- Accurate monitoring of up to four power supply voltages

- Five factory set threshold options: 1.8 V, 2.5 V, 3.0 V, 3.3 V, 5 V

- Adjustable input monitors down to 0.62 V (1.5% accuracy)

- Reset timeout: 140 ms (minimum)

- Open-drain reset output: 10 μA internal pull-up

- Reset output stage: active low, valid to IN1 = 1 V or IN2 = 1 V

- Low power consumption: 35  $\mu\text{A}$

- · Power supply glitch immunity

- Specified from -40°C to +85°C

- Package: 6-lead SOT-23

For more information on ADI's complete portfolio of supervisory products, visit www.analog.com/supervisory.

| Part<br>Number | Number of<br>Monitored<br>Voltages | Reset<br>Threshold (V)                                                                    | Min Reset<br>Timeout<br>(ms) | Reset Output Stage                               | Manual<br>Reset<br>Capability | Typical<br>Watchdog<br>Timeout (sec) | Package          | Price<br>(\$U.S.) |

|----------------|------------------------------------|-------------------------------------------------------------------------------------------|------------------------------|--------------------------------------------------|-------------------------------|--------------------------------------|------------------|-------------------|

| ADM13305       | 2                                  | 0.6 (adjustable),<br>1.68, 2.25, 2.93,<br>4.55                                            | 140                          | Active high, push-pull,<br>active low, push-pull | Yes                           | 1.6                                  | 8-lead<br>NSOIC  | 0.95              |

| ADM13307       | 3                                  | 0.6 (adjustable),<br>1.25 (adjustable),<br>1.68, 2.25, 2.93,<br>4.55                      | 140                          | Active high, push-pull, active low, push-pull    | Yes                           | _                                    | 8-lead<br>NSOIC  | 0.98              |

| ADM6710        | 3 or 4                             | 0.62 (adjustable),<br>1.58, 1.67, 2.19,<br>2.32, 2.63, 2.78,<br>2.93, 3.08, 4.38,<br>4.63 | 140                          | Active low, open-drain                           | No                            | _                                    | 6-lead<br>SOT-23 | 1.60              |

| ADM1184        | 4                                  | 0.6 (adjustable)                                                                          | 100                          | Active high, open-drain                          | No                            | _                                    | 10-lead<br>MSOP  | 2.39              |

### New Online Supervisory Selection Tools Take the Guess Work Out of Selecting the Perfect Supervisory IC for Your Design

ADI's new supervisory IC selection tools enable the design engineer to perform customized parametric searches of ADI's extensive supervisory product database. Searchable parameters include trip points, reset timeouts, watchdog timeouts, reset types, and an array of other critical features. In addition, this free downloadable tool provides a convenient cross-reference matrix between our competitors' parts and ADI's. To start using the new supervisory IC selection tool today, visit *www.analog.com/supervisory-tool*.

|                                                                                                                                   | ADI Supervisor<br>arametric Search | Electron of the local division of the local |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Settings for Single Sayer<br>Accel by Awar (10)<br>Therein (1)<br>Package Taxi<br>Carrier (1)<br>Sayer Carrier (1)<br>Package (1) | Shares                             | Annue Kint Termin (20)<br>Series Si (20)<br>Annu Congat<br>Annu Fagli (<br>Annu Fagli (<br>Congat)<br>Annu Fagli (<br>Congat)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| Approximation from (C)                                                                                                            |                                    | And a set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

For a complete list of ADI's online tools and other helpful design resources, go to *www.analog.com/designcenter*. Popular tools include:

#### ADIsimADC<sup>™</sup> www.analog.com/ADIsimADC

Simulate system behavior using many critical specifications of high speed data converters, including offset, gain, sample rate, bandwidth, jitter, latency, and both ac and dc linearity.

#### NI Multisim<sup>™</sup> Analog Devices Edition www.analog.com/multisim

Jointly developed between NI and ADI, this tool provides an intuitive environment for capturing and simulating analog circuits.

#### ADIsim0pAmp<sup>™</sup>

*www.analog.com/ADIsimOpAmp* This tool will help with the selection,

### evaluation, and troubleshooting of voltage feedback op amps.

#### ADIsimPLL<sup>™</sup> and ADIsimDDS<sup>™</sup>

#### www.analog.com/ADIsimPLL and www.analog.com/ADIsimDDS

These two circuit design tools allow the designer to simulate and evaluate complete RF circuits using either PLL or DDS frequency synthesis products.

Analog Devices, Inc.

Worldwide Headquarters

Analog Devices, Inc.

One Technology Way

P.O. Box 9106

Norwood, MA 02062-9106

U.S.A.

Tel: 781.329.4700

(800.262.5643,

U.S.A. only)

Fax: 781.461.3113

#### Analog Devices, Inc.

**Europe Headquarters** Wilhelm-Wagenfeld-Str. 6 80807 Munich Germany Tel: 49.89.76903.0 Fax: 49.89.76903.157

#### Analog Devices, Inc.

Japan Headquarters Analog Devices, KK New Pier Takeshiba South Tower Building 1-16-1 Kaigan, Minato-ku, Tokyo, 105-6891 Japan Tel: 813.5402.8200 Fax: 813.5402.1064

Analog Devices, Inc. Southeast Asia Headquarters Analog Devices 22/F One Corporate Avenue

222 Hu Bin Road Shanghai, 200021 China Tel: 86.21.2320.8000 Fax: 86.21.2320.8222

www.em.avnet.com/adi

All prices in this bulletin are in USD in quantities greater than 1000 (unless otherwise noted), recommended lowest grade resale, FOB U.S.A.

Purchase of licensed I<sup>2</sup>C components of Analog Devices or one of its sublicensed Associated Companies conveys a license for the purchaser under the Philips I<sup>2</sup>C Patent Rights to use these components in an I<sup>2</sup>C system, provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips.

©2008 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. Printed in the U.S.A. SB07448-90-4/08

www.analog.com

www.analog.com/V8Peripherals

FREE OFFER Samples and Data Sheets

# EDITED BY FRAN GRANVILLE STATE OF THE OWNER OWNER OF THE OWNER OWNER OF THE OWNER OW

# Stackable receiver enables position tracking

s transportable embedded systems become commonplace, designers are looking for economical ways to integrate globalpositioning equipment to track movements and deter theft. To target these applications, Micro/sys recently released the USB1700, a GPS (global-positioning-system)-receiver board in a form factor one-quarter the size of the PC/104 footprint. The ROHS (restriction-of-hazardous-substances) module provides designers with 12channel, WAAS (wide-area-

augmentation-system)-capable GPS functions for space-sensitive applications. The integrated GPS technology offers fast start-up and high performance in foliage-canopy, multipath, and urban-canyon environments. The board comes with a passive antenna.

The USB1700 physically conforms to a new

The new USB1700 GPSreceiver board comes in a form factor one-quarter the size of the standard PC/104 footprint.

ing and smaller packaging. To accommodate the smaller StackableUSB form factors, the company added a fifth stabilizing hole to the 104-footprint definition. Prices for the basic USB1700 start at \$230 (one).

-by Warren Webb Micro/sys Inc, www.embeddedsys.com.

form factor, which Stackable-

USB (www.stackableusb.org)

defines. StackableUSB is a

fairly recent standard that us-

es USB communications be-

tween a single-board computer and peripheral-I/O cards

in a stack similar to PC/104.

Depending on the design, the

CPU card can support 10

peripheral I/O cards-five on

the top and five on the bot-

tom-without the use of a

hub board. At  $1.85 \times 1.78$  in.,

the USB1700 is one-fourth

the size of a standard card,

resulting in improved cool-

FEEDBACK LOOP

"EDA has always

been 'broken,'

and, as long

as the technol ogy continues to

evolve, the EDA

tool designed

last year is going

to be difficult to

wield effectively

on this year's

problem."

-Web-site visitor Dave J at www.edn.com/080515p1.Add your comments.

#### AMD releases dual- and triple-core desktop processors

To bring multicore technology to desktop processors that handle multithreadeddigital-entertainment workloads, microprocessor challenger AMD (Advanced Micro Devices) recently introduced three Phenom X3 triple-core processors. With the company's 780 series chip set, the new devices allow a full HD (high-definition) experience and good gaming and digital performance.

With these processors, AMD aims to free users from the need to weigh trade-

offs between graphics and processors when purchasing a PC, given that the proliferation of digital-media devices and entertainment changes the way consumers use PCs and creates stronger demand on processing and graphics capabilities.

AMD based the multicore technology on the Direct Connect architecture, which has allowed the company to bring these triple-core desktop processors to market with benefits similar to those available with AMD's Phenom X4 quad-core processors. The triple-core processors have better performance for multitasking and multithreaded digital-media and game applications than do dual-core processors at the same clock speed, according to the company. The 2.4-GHz Phenom X3 8750, 2.3-GHz 8650, and 2.1-GHz 8450 triplecore processors sell for \$195, \$165, and \$145, respectively.

-by Ann Steffora Mutschler Advanced Micro Devices, www.amd. com.

# pulse

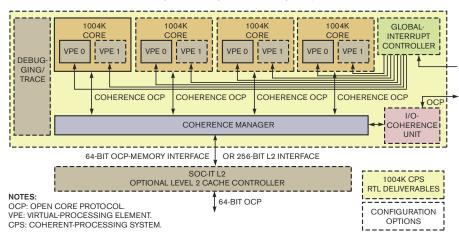

# Multiprocessor system sports as many as four coherent, multithreaded cores

IPS Technologies' multithreaded, multiprocessor, coherentprocessing MIPS32 1004K licensable-IP (intellectualproperty) platform supports as many as four single- or doublethreaded processor cores that connect through a coherence manager. The nine-stagepipeline architecture supports a worst-case 800-MHz basecore operating frequency in a 65-nm TSMC (Taiwan Semiconductor Manufacturing Co, www.tsmc.com) general-purpose process. The architecture implements a dual-core, dualthreaded configuration for a total of four threads.

32-kbyte caches for each core, a coherence manager, and a global-interrupt controller. The devices are available with 1004Kc integer and 1004Kf floating-point versions of the core, and they both support Revision 1 of the MIPS32 DSP ASE (application-specific extension). The design-time configurability of the platform allows designers to size the instruction and data caches, TLBs (translation-look-aside buffers), scratchpad RAM, and user-defined instructions. The configuration must be the same for each core in a given implementation, however, so that the architecture can support SMP (symmetric-multiproAction and data caches, TLBs, scratchpad RAM, and user-defined instructions.

cessing) operation with SMPbased operating systems, such as Open Source SMP Linux.

The multicore-coherence

The MIPS32 1004K architecture implements a dual-core, dual-threaded configuration for a total of four threads.

manager can manage one to four single- or dual-threaded cores, and it operates at the same clock rate as the cores, which also operate at the same clock rate. The coherence manager supports cache-to-cache transfers, speculative reads to external memory, and globalcache operations. It manages coherency using the MESI (modified/exclusive/shared/ invalid) protocol, and it employs redundant tags to enable L1 cache transfers and minimize the impact on processing performance. Designers configure and control the coherence scheme through globalconfiguration registers.

The platform supports an optional 256-bit interface that can manage fractional-clockrate access to an L2 memory controller. The optional I/O-coherence unit bridges noncoherent I/O-peripheral-data transfers so that the transactions are coherent within the system; it also supports per-transaction attributes for snooping L1 caches, L1 and L2 caches, noncoherent transactions, and I/O prioritization. The globalinterrupt controller can route as many as 256 system-level and interprocessor interrupts to cores or VPEs (virtual-processing elements).

The SDE (software-development environment) for this platform includes the Gnu-based MIPS SDE tool chain, the MIPSsim bus-functional modeling and instruction-set simulator, and the enhanced-JTAG and PDtrace system-navigator probe with coherence awareness. The two initial versions of this core, the integer 1004Kc and the floating-point 1004Kf, will be available for licensing this quarter.

-by Robert Cravotta

MIPS Technologies, www.

mips.com.

The architecture also has

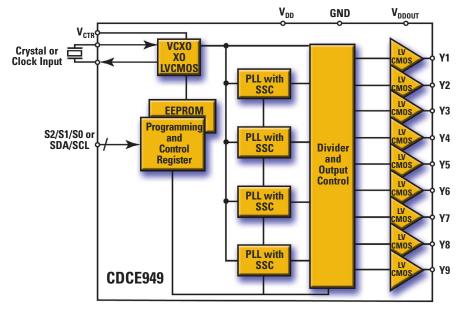

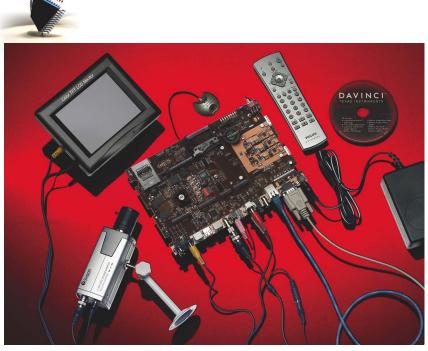

# **Flexible Clock Generators**

### Multiple I/O-V and Programmability Ease System Design

#### - High-Performance Analog>>Your Way™

#### Applications

- Digital media systems (audio/video)

- GPS receivers

- TI DSP, OMAP™ and DaVinci™ media processors

#### **Features**

- Spread Spectrum Clocking (SSC) reduces affects of EMI

- I<sup>2</sup>C and EEPROM programmability

- On-chip Voltage Controlled Crystal Oscillator (VCXO)

Texas Instruments provides a portfolio of low-power, low-jitter, programmable clock generators capable of generating up to nine output clocks from a single input frequency. This level of functionality provides you with capabilities previously unavailable in clock/timing products.

| Device   | Supply Voltage (V) | I/O Voltage (V) | # of PLL | # of Outputs | Output Frequency (MHz) | Temperature Range (°C) | Package (TSSOP) |

|----------|--------------------|-----------------|----------|--------------|------------------------|------------------------|-----------------|

| CDCE949  | 1.8                | 2.5/3.3         | 4        | 9            | 230                    | -40 to +85             | 24              |

| CDCE937  | 1.8                | 2.5/3.3         | 3        | 7            | 230                    | -40 to +85             | 20              |